研究方向1:三维纳米电路的制造性设计方法EDA技术

芯片采购网专注于整合国内外授权IC代理商现货资源,芯片库存实时查询,行业价格合理,采购方便IC芯片,国内专业芯片采购平台。

进入纳米工艺节点,电路的物理结构对工艺容量和设计提出了新的挑战。可制造性和成品率已成为集成电路高端芯片批量生产和盈利的最关键因素之一EDA该技术搭建了沟通电路设计与工艺制造的桥梁,可系统地提高纳米芯片的良率和性能。

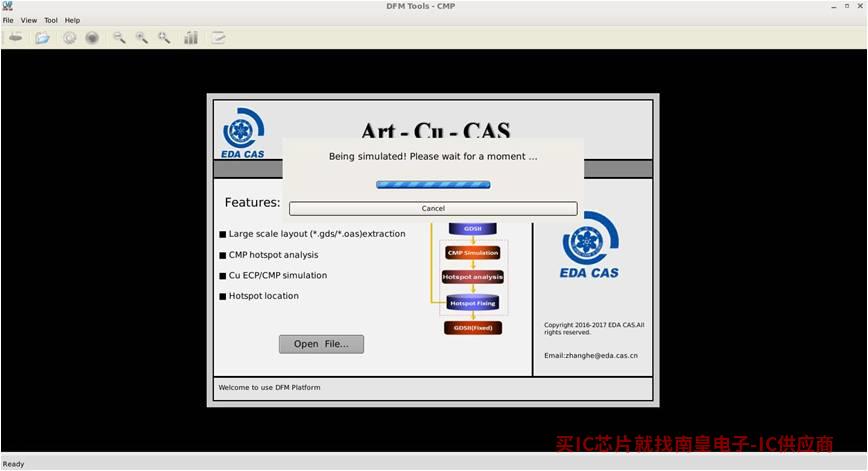

针对集成电路先进工艺制造和设计中存在的基性和前瞻性核心问题,实验室开展了三维纳米电路制造设计方法和EDA具有自主知识产权的基础理论和关键技术研究,构建纳米加工设计协同优化DFM实现工艺热点检测和寄生参数提取的全套解决方案,软件平台,实现新一代集成电路设计的关键技术EDA创新和突破工具。研究内容包括制造设计、三维纳米芯片CMP建模理论和方法,建模图形效应,智能填充冗余金属,EDA并行计算、全芯片热点检测和优化等关键技术。

研究成果:

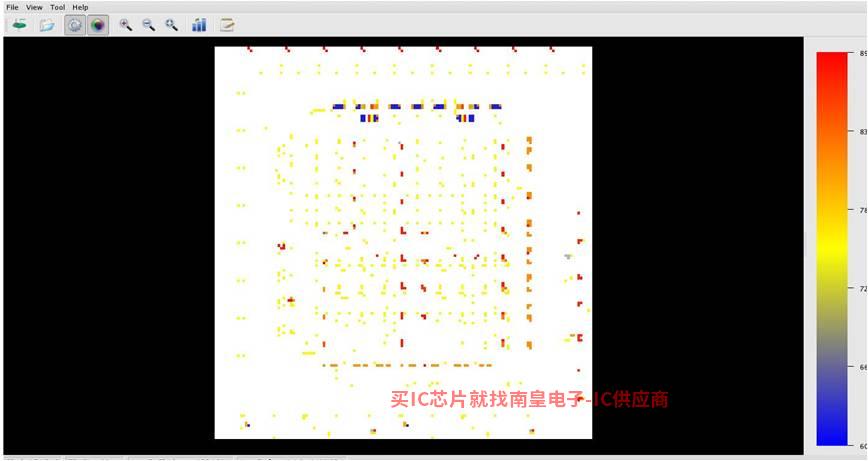

三维纳米电路的制造性设计方法EDA技术研究创新地建立了纳米尺度芯片多物理场CMP工艺仿真模型和设计优化技术构建了纳米加工与设计的协同作用ArtDFM满足大型纳米芯片的参考流程和软件平台DFM技术需求。Art系列DFM该软件包括行业首款32/28nm HKMG CMP模拟工具与纳米节点铜互连CMP仿真工具,主流布局格式(GDSII、OASIS等)快速处理,提取地图参数,智能填充冗余金属,CMP工艺模拟、热输出与反标、第三方应用集成等功能。Art系列DFM该软件支持多核架构自适应并行计算,其运算速度和精度达到行业先进水平,各项指标达到行业使用标准,已应用于国内知名设计制造企业,为其提供全芯片热点检测和表面平整度预测服务。

纳米芯片DFM平台

平面模拟热点检测

研究方向2:高频电磁场分析及仿真技术

研究方向重点关注高频电磁场算法基础研究、算法应用研究和算法工具开发,研究内容主要包括电磁和多物理耦合场多层建模仿真优化技术、电磁和多物理分析模型降级算法、无线通信通道建模技术和物联网定位应用。

研究成果:

在基于广义本征分解的集成电路互连系统高效物理建模研究中,实现了广义本征分解方法(PGD)以及棱镜单元静磁场的计算PGD方法。正交本征分解降级方法正交本征分解方法(POD)与参数空间维数的增加相比,PGD优势逐渐凸显。以模拟低通滤波器的数值试验为例,PGD比迭代扫频计算节省90%以上的计算时间。

为了提高室内毫米波无线通信定位混合系统的定位精度,使用它watersheds、主要成分分析和人工神经网络实现了对LOS和NLOS波束识别。毫米波束的识别是第一个。

在并行计算研究中,结合任务级和数据级并行,提高了地图参数的提取效率。实现了网格分割优化技术GDSII采用版图解析获得的几何结构文件Tetgen/Gmsh等开源包进行网格切割,并借助自动网格加密加速提取版图参数。

研究小组利用模型降级及其在电磁数值分析中的应用研究C 编程实现了POD/PGD这两种模型降级串行工具利用模型降级中的模型作为一个相对独立的任务级并行,利用数据级并行算法研究一维和二维参数空间中的全波问题。该计算表明,POD与PGD可以得到相当准确的解决方案,从而获得结构共振模态。

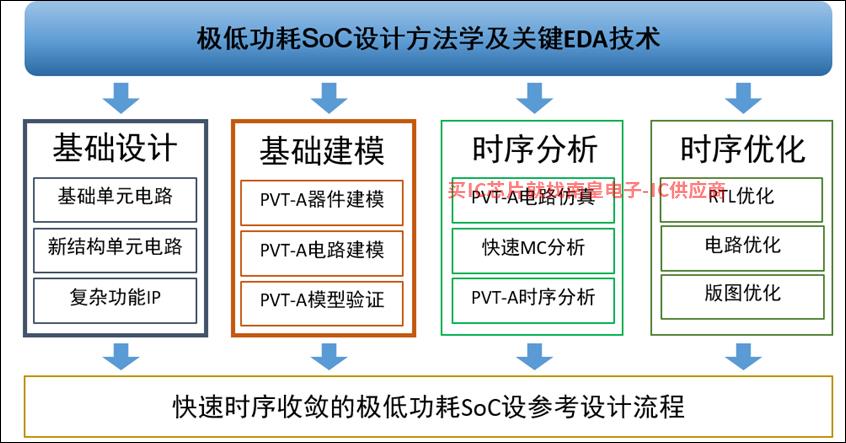

研究方向3:亚阈值低功耗设计方法EDA技术

该研究旨在研究亚阈值极低功耗SoC在移动物联网和体域网的应用中,设计方法、研发和设计亚阈值SoC极低功耗IP,并为对应SoC设计研究的关键EDA技术。主要研究PVT-A在偏差下,高鲁棒性亚阈值AllegroMicroSystems代理低功耗SoC设计方法和关键优化技术主要包括设备、地图、电路和架构之间的跨层协同设计和优化、亚阈值极低功耗基础单元、新型结构电路和复杂功能IP的设计,PVT-A变化敏感情况的设备建模、电路建模和模型验证技术,功耗极低SoC快速统计分析和优化技术,高鲁棒可重构异步亚阈值极低功耗SoC开发相关核心算法和设计技术EDA软件原型。

功耗极低的亚阈值SoC设计方法及关键EDA技术框架

研究成果:

EDA亚阈值中心功耗极低SoC设计方法及关键EDA在技术领域开展了多年的研发工作,研究设计了亚阈值温度传感器和32位亚阈值SAPTL超前进位加法器,16位亚阈值B-SAPTL加法器、16x16亚阈值ASYN-B-SAPTL异步乘法器、动态可重构亚阈值逻辑等极低功耗电路IP,技术指标优于文献报道的类似功能电路,开发了单元电路布局微调软件、电路结构自动评价工具、电路设备参数优化工具、快速High-σ蒙特卡洛分析工具、设备建模工具PVT敏感的单元电路特工具等。

研究方向四:支持数千万门高速并行SPICE后仿真技术

现有SPICE虽然模拟工具的算法不同,但它们通常是基于CPU通用软件算法,寻求先进工艺的超大量设备模型,超大规模电路矩阵,特别是RC因为矩阵CPU由于架构和运算单元的限制,整体运算效率已不能满足先进工艺设计的需要。

在系统架构层面构建新的模拟验证方案的基础上GPU/CPU开发晶体管级后异构平台高精度模拟工具。通过模拟算法的分解,结合相应的特殊硬件架构,适应模拟算法的特点,通过软硬件协调,最终实现现有模拟工具的数量级以上模拟加速效果,支持更大、更复杂的模拟验证设计,完成原模拟工具无法完成的模拟验证任务。

研究成果:

到2020年底,开发的仿真工具性能已达到主流工具的4~6倍。