异构和异构最近越来越流行multi-die 2.5D封装技术促进了一种新的界面,即超短距离(ultra-short reach:USR),其电气特性及传输STC代理统一印刷电路板的布线差别很大。需要使用长而损坏的连接SerDes IP串行通信通道,短距离接口支持并行总线系统结构。

芯片采购网专注于整合国内外授权IC代理商现货资源,芯片库存实时查询,行业价格合理,采购方便IC芯片,国内专业芯片采购平台。

SerDes需要端接信号(50) ohm),尽量减少反射,减少远端串扰,从而增加功耗。2.5D无需端接封装内的电气短路接口。相比于“recovering在串行数据流中嵌入时钟并恢复相关时钟数据(CDR)对于电路面积和电源,这些并行接口可以采用更简单的时钟转发电路设计,使提供传输的时钟信号具有一组N数据信号。

该接口的另一个优点是大大降低了芯片之间的静电放电保护(ESD)电路设计要求。内部封装连接将较低ESD节省了大量的电压应力约束I / O电路面积(并显著减少)I / O寄生效应)。

2.5D裸片之间独特的接口设计需要驱动使用小芯片SerDes链接的全芯片设计费用。然而,到目前为止,已经有很多用于这些USR接口的电路和物理实现方法。

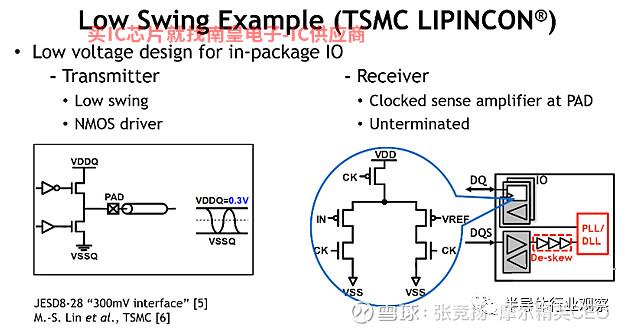

最近举行的VLSI 在2020年研讨会的邀请演讲中,台积电提出了他们关于并行总线和时钟转发架构的建议LIPINCON该架构为low-voltage, in-package interconnect缩写。本文简要回顾了演示文稿的重点。

短距离接口设计的关键参数是:

每个引脚的数据速率:取决于接线长度/插入损耗、功耗、所需的电路时序裕度

总线宽度:模块化定义子通道

能效:是的pJ /单位不仅包括I / O驱动器/接收器电路还包括任何其他数据提取/排队和/或编码/解码逻辑

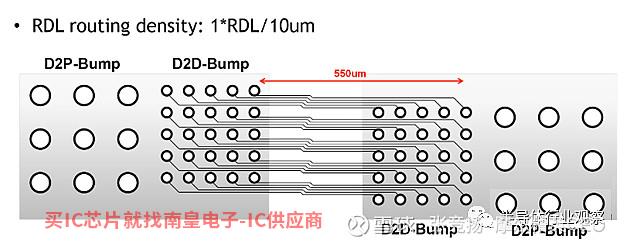

“Beachfront(线性)和面积效率:测量小芯片上每个线性边缘和面积周长的总数据带宽,即Tbps / mm和Tbps / mm ** 2;取决于信号凸点间距和2.5D基板上金属再分布层的数量和间距定义了可以布线信号线的凸点行数–请参见下图

延迟:另一个性能指标;数据传输启动与接收之间的时间,以传输周期的单位间隔为单位

架构师正在寻求最大化总数据带宽(总线宽度)*数据速率),同时实现非常低的每个功耗。小芯片接口在多个处理器(或SoC)处理器是内存还是处理器?I / O这些关键的设计措施适用于控制器功能之间。

下图显示了台积电LIPINCON IP定义的关键特征。

DLL相位检测器(低通滤波器)中的回路XOR形成型逻辑,检测器将输入时钟与链的最终输出进行比较。与链输出的先进或滞后特性相比,可调节逆变器控制电压。因此,链的总延迟与输入时钟密切相关。DLL输入时钟信号特定相位的输出提供链中各级(相等)延迟。在接收器触发器中使用适当的相位输出捕获并行数据,这是一种补偿接口上任何数据到时钟偏移的方法。

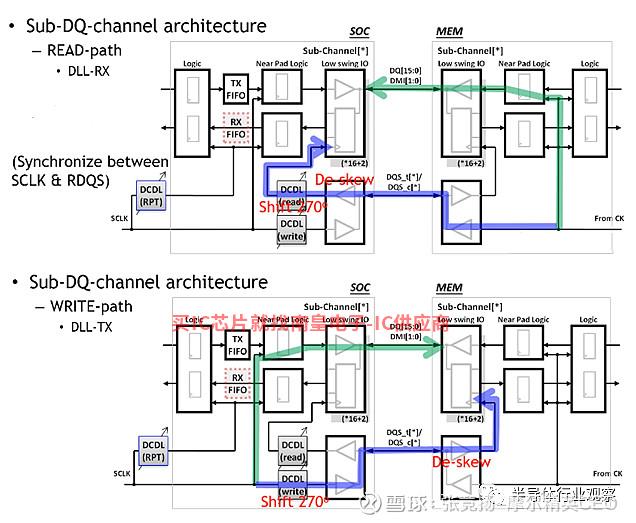

台积电IP团队针对SoC在内存界面的具体情况下,开发了一种创新方法。存储器的小芯片不一定需要嵌入DLL捕获信号输入。对于非常宽的接口,例如,将512个地址和256个数据位分为多个子通道-成本敏感存储芯片DLL电路的成本会很高。如下图所示,在SoC中出现了DLL相位输出用作存储器写周期的输入选通脉冲。(图中还显示了存储器读取路径,说明如何连接存储器的数据选择脉冲read_DLL电路输入。)

台积电的演讲提到,他们的一些客户已经是USR界面设计开发了自己的界面设计IP实现。示例显示了一个非常低的摆幅(0.2V)以地面为参考的电气定义(如信号摆幅高于或低于地面)。

但是,对于寻求利用高级包装而没有设计资源自行开发芯片接口电路的无晶圆厂客户来说,TSMC LIPINCON IP定义是一个非常有吸引力的选择。此外,坦白地说,考虑到台积电的支持,这个定义可能有助于加速捕获IP标准电气定义和小芯片设计市场机会

作者:张竞扬-摩尔精英CEO

链接:https://xueqiu.com/4927163759/152609671

来源:雪球

作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

- 普遍计算的六个必要条件

- Imagination和Ambarella(安霸半导体)联合开发ASIL自动驾驶汽车人机界面可视化技术

- 智芯山居改造大赛获奖队公布

- 在德国科技帮助艾灵网络加速智能仓储行业的5个G专用网络部署

- Aqara出现在三星开发者大会上,与三星携手共推Matter协议发展

- 联发科太会制造旗舰处理器了!天竺9200安兔在室温下跑分超过126万

- 欧盟可能会加速光伏建筑安装 IGBT产业链有望受益

- ST:碳化硅技术的发展 关键在于控制整个产业链

- 如何选择合适的开关电源?MOSFET?

- 在拒绝美国并坚持与中国公司合作后,巴西迎来了好消息,即将应用5G技术

- e任命新副总裁,进一步加强电子商务平台战略

- 首个万台级5G今日小基站招标开标:5G建设拐点初显,创新不断涌现