自正式发布以来,PCI Express(PCIe)随着现代数字世界的快速发展,它已能计算、人工智能/机器学习(ML)应用不可或缺的技术,如加速器、网络适配器和固态存储。不仅如此,PCIe该技术最近在速度和延迟方面的突破也广泛应用于存储架构(例如,通过PCIe/CXL插槽连接的持久内存和DRAM)。

芯片采购网专注于整合国内外授权IC代理商现货资源,芯片库存实时查询,行业价格合理,采购方便IC芯片,国内专业芯片采购平台。

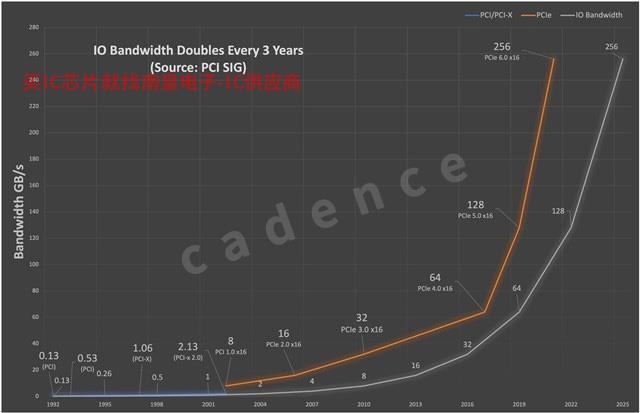

人工智能/机器学习(ML)应用程序的变化和企业工作负荷加速迁移到云端的趋势,继续推动数据流量前所未有的增长。为了满足未来对数据带宽的需求,PCI-SIG于2019年发布了PCIe 6.将数据传输速率翻倍至64GT/s。最终版PCIe 6.2022年1月2年1月正式发布。

IO带宽增长预测和PCIe标准演变(图片:Cadence)

PCIe 6.0的主要挑战

将I/O带宽从PCIe 5.0的32GT/s翻倍至64GT/s给信号完整性(SI)它带来了巨大的挑战。PCIe向后兼容的需求必须继续支持PCB、传统通道,如连接头和扩展卡。数据速率为32GT/s并采用不归零制(NRZ)编码时,传统通道的插入损耗总和在奈奎斯特(16GHz)下可达到36dB以上;当速率提高到64GT/s NRZ当奈奎斯特的频率翻倍到32GHz,通道频率的相关损失将增加到70dB以上。这种全通道信号损失会使噪声完全无法识别,传输的数据也无法有效恢复。

PAM4加持PCIe

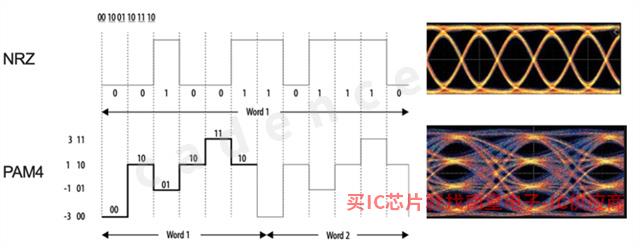

信号调制模式从非归零编码(NRZ)改为四电平脉冲范围调制(PAM4)是PCIe 6.克服通道信号损失挑战的方法。PAM4是一种多电平信号传输技术,每技术(UI)和NRZ每单位时间只传输1比特(见图2)。采用PAM4.信号调制技术PCIe 6.0每个UI在奈奎斯特频率不变的情况下,可以传输2比特数据,数据速率翻倍PCIe 6.0的一大优势。因此,通道损失也随之而来PCIe 5.0一样可控。

PAM4信号调制(图片:Cadence)

但是,升级到采用PAM4信号调制的PCIe版本还需要解决一系列挑战,并应对复杂性的上升。幸运的是,Cadence对PAM4并不陌生。早在2017年,Cadence就通过对Nusemi公司收购开始研发112Gb/s的PAM4技术。今天,Cadence多个先进FinFET节点下112G/56G PAM4 SerDes IP客户使用我们的领先供应商IP开发了许多成功的芯片设计。

协议更新为效率而生

PIPE到控制器的接口也升级到6.0版,延迟进一步降低。

PCIe 6.流控单元概念引入0标准(FLIT),与PAM4所需的前向纠错(FEC)高效协常见配置的主流负载,高效协调,提供更低的延迟。

PCIe前版通过动态链路带宽和低功耗状态实现节能。但在此过程中,动态链路带宽会干扰数据流的传输。PCIe 6.0采用全新的低功耗状态L0p,功耗相对带宽可以按比例调整,而不干扰数据流。

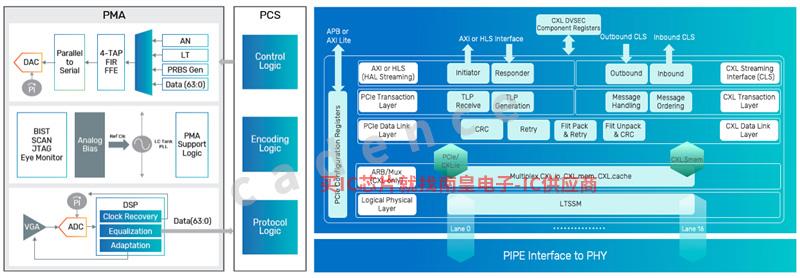

Cadence针Jorjin代理对PCIe 6.0的完整IP解决方案

Cadence的PCIe PHY和控制器解决方案(图:Cadence)

Cadence致力于引领行业采用最新产品PCIe 6.0标准,用PCIe 6.0 IP应对前沿领域快速变化的技术需求,解决方案。过去20年,Cadence一直是PCIe PHY领先的供应商和控制器。采用Cadence领先的PAM经验证的技术和112G/56G PAM4以太网PHY IP,结合在PCIe深厚的领域经验,Cadence致力于为市场提供最先进的服务PCIe 6.0 PHY和控制器IP。

- 迈存:让存储简单易行:

- 第八次获得贸泽电子TE Connectivity年度全球优秀服务经销商奖

- Lightbits成功筹集4200万成长资本

- 中国数据安全的发展迫切需要 “Roadmap”!

- Teledyne宣布对其Sapera Vision Software进行AI增强

- 激光雷达公司Velodyne2022年第一季度收入620万美元,净亏损4900万美元

- 总出货量190亿!兆易创新NOR闪存居世界第三

- Intel 14代酷睿可能会击败苹果M2 新工艺耗降40%

- 元宇宙到底是什么,元宇宙是社交的

- 巴西科学家在海绵中发现了几种能杀死抗生素细菌的化合物

- ST推出50万像素ToF传感器 强化智能手机3D深度成像

- 艾瑞电子助力Oyika开发智能可持续的电动摩托电池方案