近20 近年来,随着数字通信的快速发展,信号链路中的模数转换器(ADC)其作用越来越重要。超高速宽带ADC 可广泛应用于卫星、雷达、电子战、数字示波器、通信等接收机领域。传统高速8位ADC 虽然结构转换速度快,但电路规模随分辨率而变化n 呈2n 指数增长[3,4],功耗大。折叠/ 插值型结构ADC 并行比较器的数量可以通过折叠和插值转换来大大降低,转换速率相当于整个并行结构。然而,即使采用双极工艺,折叠结构电路仍然受到设备失配的影响。幸运的是,前端数字校准算法可以用来降低设备失配对电路性能的影响。

芯片采购网专注于整合国内外授权IC代理商现货资源,芯片库存实时查询,行业价格合理,采购方便IC芯片,国内专业芯片采购平台。

折叠/ 插值型ADC 前端数字校准算法可以纠正设备失配,但校准动态时钟抖动误差需要很大的成本。因此,折叠/ 插值型ADC 前端一般采用高速宽带采样保持电路(S/H),采样时钟抖动的影响可以有效降低。本文提出了一种基于0的基础.18 μm BiCMOS采用简单的数字校准算法,可以大大降低电路的增益误差和失衡误差。电路模拟和实际测试表明,在通过数字校准采样保持电路增益和失衡误差后,ADC 动态性能可提高10 dB 以上。

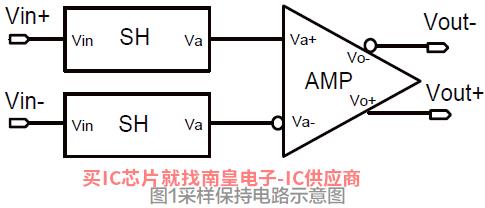

1 采样保持电路设计

采样保持电路采样率达到2GSPS,所以S/H 电路采用开环结构。S/H 电路系统由采样保持等级(SH)电路和放大和驱动级(AMP)电路组成。

图9 Fin=484MHz, Fs=2GSPS下ADC的SFDR

5 结论

本文提出的基于0.18 μm BiCMOS 工艺设计的高速宽带采样保持电路,成功应用于8 高速折叠/ 插值ADC 中,大大提高ADC 动态性能和输入带宽。采样保持电路开环结构,工作转换Azoteq代理速率超过2GSPS,利用增益和失衡数字校准算法提高电路的静态和动态性能。ADC 电路试验结果优异,说明设计的高速宽带采样保持电路满足要求。

参考文献:

[1] YU J S, ZHANG R T,ZHANG Z P,et al.A digital calibration technique for an ultra high-speed wide-bandwidth folding and interpolating analog-to-digital converter in 0.18-μm CMOS technology[J]. Journal of Semiconductors,2011,32(1):977.

[2] FLYNN M P,SHEAHAN B.A 400-Msample/s,6-b CMOS Folding and Interpolating ADC[J].IEEE Journal of Solid- State Circuit,1998,33(12):1932.

[3] LEE D, SONG J,SHIN J,et al.Design of a 1.8V 8-bit 500MSPS Folding-Interpolation CMOS A/D Converter with a Folder Averaging Technique[C].18th European Conference on Circuit Theory Design,2007:356.

[4] ALI A M, MORGAN A,DILLON C,et al.A 16 b 250MS/s IF-sampling pipelined A/D converter with background calibration[C].IEEE International Solid-State Circuit Conference Digest of Technical Papers,2010:292.

[5] CHU M, JACOB P,KIM J-W,LeRoy M R,et al.A 40Gs/s Time Interleaved ADC Using SiGe BiCMOS Technology[J]. IEEE Jouurnal of Solid-State Circuit,2010,45(2):380.

(本文来源《IC2022年5月,代理杂志

- 格芯获得3000万美元政府基金研发GaN芯片

- R&S携手高通在NAB 2022展会上演示智能手机的端到端5G流媒体直播

- 筑波科技与美商Teradyne合作ETS设备 了解半导体车用市场趋势

- 完成光微技术B一轮数亿元融资加速ToF芯片和传感器量产落地

- NVIDIA矿卡崩溃预警:可能会影响性能

- 欧菲光被释放为黑名单 营收腰斩

- 从华为手中抢徕卡,小米能得到什么?

- Software République2022年巴黎车展上出现了安全智能的电动汽车充电站

- 全球首创!Apollo超过1500万像素车载摄像头

- 新能源大变革背后

- 物联网智能家居安全从,谈物联网智能家居安全

- 巴西将开始使用5G华为可能会有更多的技术机会